# A Fully Synthesizable Digital Low Dropout Regulator(LDO) with Fast Transient Response

Wei-Cheng Wang and Po-Hung Chen

Institute of Pioneer Semiconductor, National Yang Ming Chiao Tung University, Hsinchu, Taiwan.

### Introduction

- □Low Dropout Regulator(LDO)

- The purpose of LDO is to provide stable supply voltage for the back-end circuits.

- □Comparisons of digital and analog LDOs

|                                        | Digital LDO | Analog LDO     |  |

|----------------------------------------|-------------|----------------|--|

| Dropout Voltage                        | Low         | Medium to High |  |

| Benefits from<br>Technology<br>Scaling | More        | Fewer          |  |

| Settling Time                          | Fast        | Slow           |  |

| Output Ripple                          | Large       | Small          |  |

| Quantization<br>Error                  | Yes         | No             |  |

- □Internet of thing(IoT) needs low supply and small area, digital LDO is a suitable choice.

- □When the load current changes, digital LDO has faster transient response.

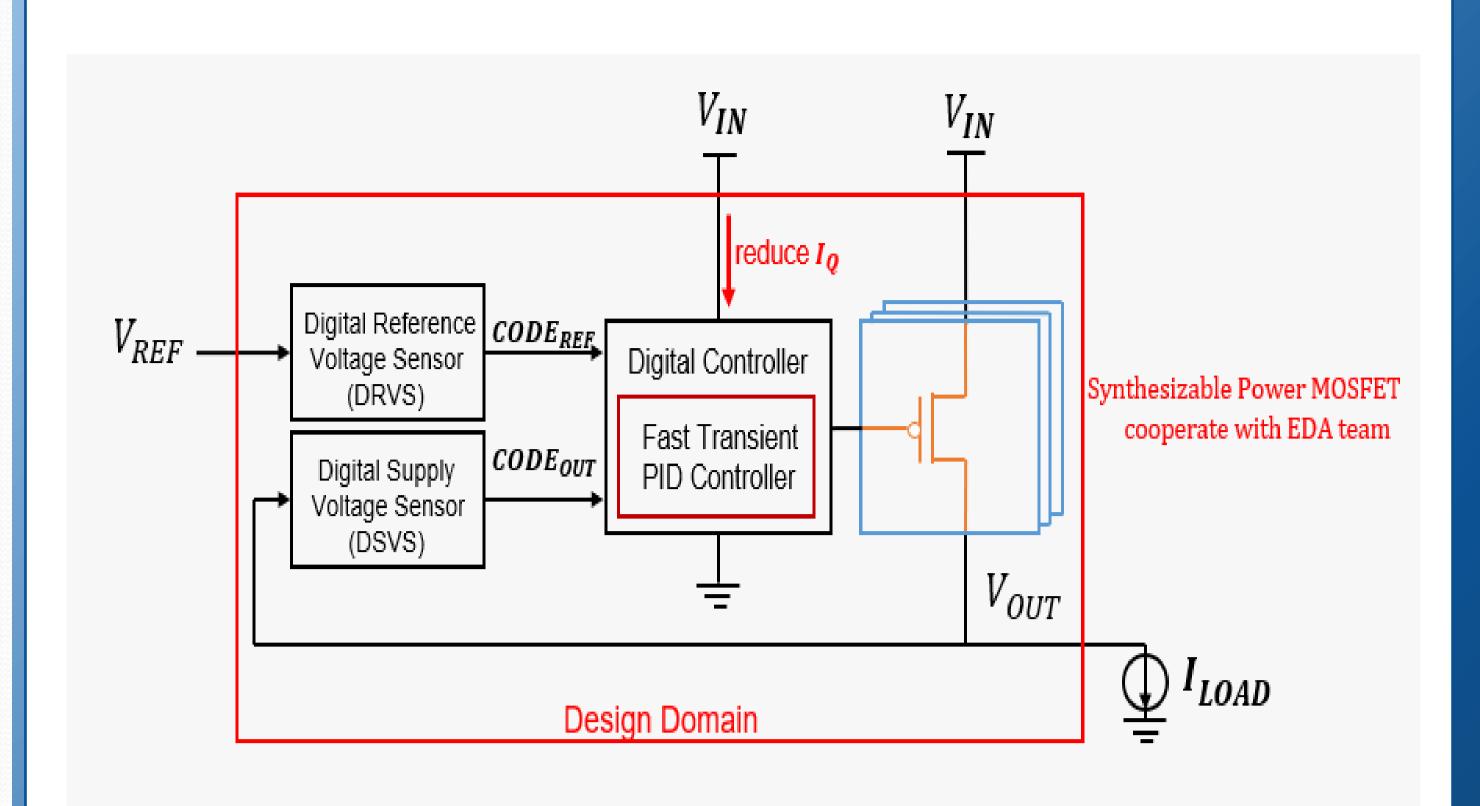

## System Architecture

- □The Digital Reference Voltage Sensor and Digital Supply Voltage Sensor will transfer voltage to digital code.

- □ The Digital Controller will turn on/off the power MOSFET according to the comparison result of *CODEout* and *CODEREF*.

- □We will cooperate with EDA team to make the power MOSFET synthesizable.

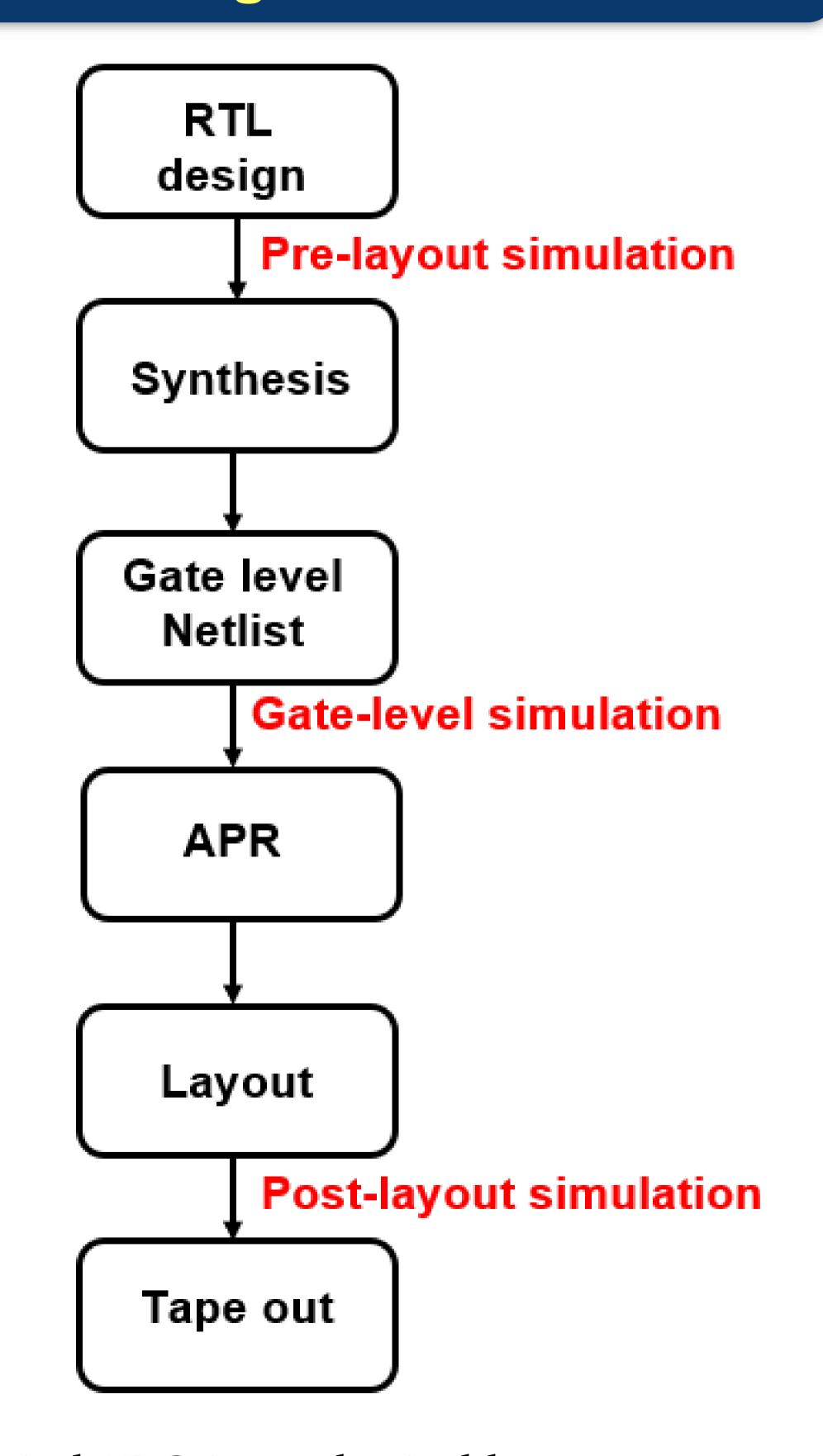

#### **Design flow**

- ☐ The whole digital LDO is synthesizable.

- □The design flow will be similar with digital circuit design.

- ☐ APR stands for automatic placement and routing.

## Specification

☐ The target of this work and the achievement of other works.

|                                                       | This work      | [1] ISSCC 2020  | [2] VLSI 2019    |

|-------------------------------------------------------|----------------|-----------------|------------------|

| $V_{IN}$                                              | 0.9V           | 0.7 to 1.05 V   | 0.5 to 1V        |

| $V_{out}$                                             | 0.45 to 0.7V   | 0.65 to 0.95V   | 0.45 to 0.9V     |

| Peak current efficiency<br>@I <sub>L</sub>            | > 99%<br>@1A   | 98.6%<br>@3A    | 99.9%<br>@0.1A   |

| Current efficiency $@I_L$ (light load current)        | > 90%<br>@0.1A | 74%<br>@0.1A    | 95%<br>@1mA      |

| $egin{aligned} V_{DROOP} \ @\Delta I_L \end{aligned}$ | < 150mV<br>@1A | 200mV<br>@1.17A | 94.1mV<br>@124mA |

| $I_Q$                                                 | < 15mA         | 43mA            | 0.68mA           |

| Fully Synthesis                                       | yes            | yes             | no               |

| FoM                                                   | < 2ps          | 5.2ps           | 4.3ps            |

$$FoM = I_Q \times (\frac{C_{out} \times V_{DROOP}}{\Delta I_L^2} + \frac{0.5}{SR})$$

, where  $SR = \frac{\Delta I_L}{\Delta t}$

- Optimizing the performance of transient response is the target of this work.

- □Another target is to reduce the quiescent current of the digital controller, making current efficiency better.

#### References

- □ [1] Suyoung Bang, Wootaek Lim, Charles Augustine, Andres Malavasi, Muhammad Khellah, James Tschanz, Vivek De, "A Fully Synthesizable Distributed and Scalable All-Digital LDO in 10nm CMOS," IEEE ISSCC, February 2020

- □ [2] S. J. Kim et al., "A 0.5-1V Input Event-Driven Multiple Digital Low-Dropout-Regulator System for Supporting a Large Digital Load," *IEEE Symp. VLSI Circuits*, pp. C128-C129, June 2019.